企業(yè)博客

更多>>

首頁(yè)常見(jiàn)問(wèn)題 差分晶振HCSL驅(qū)動(dòng)器輸出結(jié)構(gòu)

差分晶振HCSL驅(qū)動(dòng)器輸出結(jié)構(gòu)

來(lái)源:http://www.fengxong.cn 作者:康比電子 2019年06月29

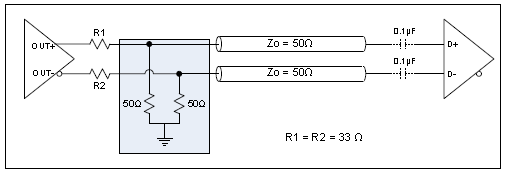

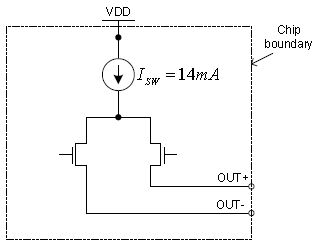

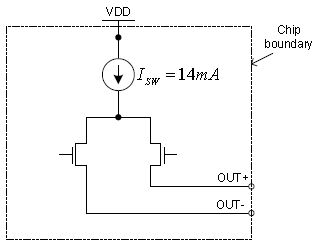

HCSL驅(qū)動(dòng)器選項(xiàng)僅在某些SiTime差分晶振系列中可用.HCSL輸出結(jié)構(gòu)(見(jiàn)圖1和圖3)由14毫安開(kāi)關(guān)電流源驅(qū)動(dòng),通常通過(guò)50Ω電阻接地.如圖2所示,標(biāo)稱(chēng)信號(hào)擺幅為700毫伏.輸出端的開(kāi)漏晶體管在幾千歐姆范圍內(nèi)具有相當(dāng)高的阻抗.從交流角度來(lái)看,輸出晶體管阻抗與50Ω負(fù)載電阻并聯(lián),導(dǎo)致等效電阻非常接近50ω.由于該接口中使用的走線(xiàn)具有50Ω的特性阻抗,負(fù)載反射的任何信號(hào)都將在源端被吸收.通常,兩個(gè)小電阻R1和R2(見(jiàn)圖2)與高阻抗驅(qū)動(dòng)器串聯(lián)放置.它們通過(guò)減緩輸出電流的快速上升起到過(guò)沖限制器的作用,對(duì)源阻抗匹配沒(méi)有影響.SiTime推薦這些電阻使用33Ω電阻.

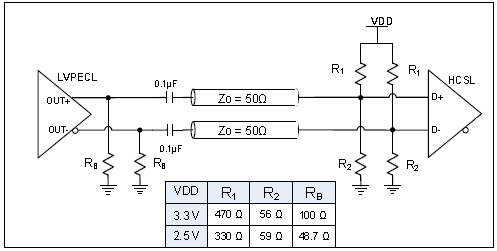

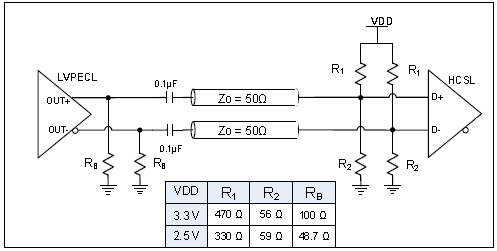

典型的HCSL接口使用電流模式驅(qū)動(dòng)器,在源端使用50Ω至GND端接,在接收器端不使用端接.此外,對(duì)于HCSL輸出驅(qū)動(dòng)器,LVPECL差分晶振驅(qū)動(dòng)器可用于驅(qū)動(dòng)HCSL輸入.圖3顯示了驅(qū)動(dòng)帶LVPECL輸出的HCSL接收機(jī)的推薦端接原理圖.為了滿(mǎn)足HCSL接收機(jī)要求的750毫伏的VOH電平和0V的VOL電平,它采用交流耦合電容來(lái)分離源和負(fù)載偏置電壓.

負(fù)載側(cè)的戴維寧等效端接也在接收器輸入端設(shè)置適當(dāng)?shù)墓材k妷?電阻BR為L(zhǎng)VPECL驅(qū)動(dòng)器提供適當(dāng)?shù)腄C偏置.對(duì)于2.5V和3.3V工作電壓,推薦的端接網(wǎng)絡(luò)元件值如圖3所示.

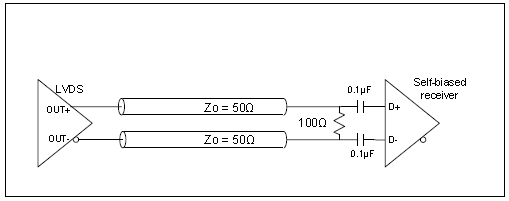

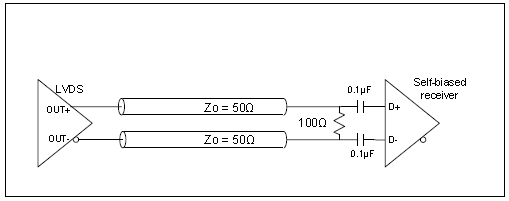

許多差分接收機(jī)具有片內(nèi)DC偏置電路和/或終端網(wǎng)絡(luò).在這種情況下,振蕩器輸出應(yīng)該交流耦合.如果需要外部偏置,應(yīng)根據(jù)接收器器件的數(shù)據(jù)表進(jìn)行設(shè)計(jì).

LVDS或LVPECL振蕩器可用于驅(qū)動(dòng)自偏置差分輸入.LVDS輸出晶振需要更少的無(wú)源元件和更低的運(yùn)行功率.如果700毫伏的LVDS擺幅對(duì)接收機(jī)來(lái)說(shuō)足夠了,最好使用LVDS振蕩器.圖5顯示了LVDS振蕩器與自偏置差分接收器的接口.

圖1:HCSL驅(qū)動(dòng)器輸出結(jié)構(gòu)

圖2:HCSL接口終端

5.用LVPECL振蕩器驅(qū)動(dòng)HCSL接收機(jī)典型的HCSL接口使用電流模式驅(qū)動(dòng)器,在源端使用50Ω至GND端接,在接收器端不使用端接.此外,對(duì)于HCSL輸出驅(qū)動(dòng)器,LVPECL差分晶振驅(qū)動(dòng)器可用于驅(qū)動(dòng)HCSL輸入.圖3顯示了驅(qū)動(dòng)帶LVPECL輸出的HCSL接收機(jī)的推薦端接原理圖.為了滿(mǎn)足HCSL接收機(jī)要求的750毫伏的VOH電平和0V的VOL電平,它采用交流耦合電容來(lái)分離源和負(fù)載偏置電壓.

負(fù)載側(cè)的戴維寧等效端接也在接收器輸入端設(shè)置適當(dāng)?shù)墓材k妷?電阻BR為L(zhǎng)VPECL驅(qū)動(dòng)器提供適當(dāng)?shù)腄C偏置.對(duì)于2.5V和3.3V工作電壓,推薦的端接網(wǎng)絡(luò)元件值如圖3所示.

圖3:LVPECL至HCSL接口6利用LVPECL振蕩器驅(qū)動(dòng)共模抑制接收機(jī)

大多數(shù)SiTime差分振蕩器沒(méi)有CML輸出選項(xiàng),但它們可以使用LVPECL驅(qū)動(dòng)器驅(qū)動(dòng)CML接收器.在這種情況下,端接原理圖必須確保接收器輸入端的單端電壓擺幅為400毫伏,VDD共模電壓為200毫伏[2】.圖4顯示了驅(qū)動(dòng)帶LVPECL輸出的CML接收器的推薦端接原理圖.由于LVPECL和CML共模電壓之間的巨大差異,DC電流隔離需要耦合電容.電阻RB用于LVPECL差分晶體驅(qū)動(dòng)器的適當(dāng)偏置.接收器端的戴維寧等效端接設(shè)置適當(dāng)?shù)钠秒妷?并與RB電阻一起確保適當(dāng)?shù)男盘?hào)擺幅.

圖4:LVPECL至CML接口

7個(gè)自偏置差分輸入許多差分接收機(jī)具有片內(nèi)DC偏置電路和/或終端網(wǎng)絡(luò).在這種情況下,振蕩器輸出應(yīng)該交流耦合.如果需要外部偏置,應(yīng)根據(jù)接收器器件的數(shù)據(jù)表進(jìn)行設(shè)計(jì).

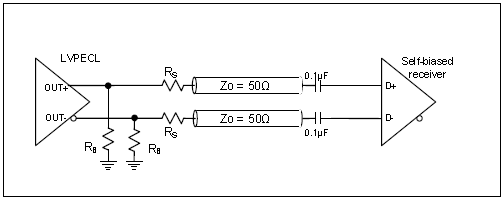

LVDS或LVPECL振蕩器可用于驅(qū)動(dòng)自偏置差分輸入.LVDS輸出晶振需要更少的無(wú)源元件和更低的運(yùn)行功率.如果700毫伏的LVDS擺幅對(duì)接收機(jī)來(lái)說(shuō)足夠了,最好使用LVDS振蕩器.圖5顯示了LVDS振蕩器與自偏置差分接收器的接口.

圖5:帶有內(nèi)部端接和偏置的LVDS驅(qū)動(dòng)器與自偏置差分接收器的連接

LVPECL輸出可以在接收器上產(chǎn)生高達(dá)1.6V的差分晶振擺幅.圖6顯示了LVPECL振蕩器與自偏置差分接收器的連接示意圖.電阻RS在負(fù)載端產(chǎn)生一個(gè)分壓器.接收器輸入端的電壓擺幅可以通過(guò)選擇RS值來(lái)設(shè)置.RB為L(zhǎng)VPECL驅(qū)動(dòng)器提供DC偏置電流,其值可以從等式1計(jì)算.請(qǐng)注意,接收器將看到有效端接電阻值為RS+50Ω.

圖6:LVPECL驅(qū)動(dòng)器與帶內(nèi)部端接和偏置的自偏置差分接收器的連接.

為了保持信號(hào)的完整性,遙感器和銣應(yīng)放置在傳輸線(xiàn)之前,盡可能靠近石英晶體振蕩器.負(fù)載端終端網(wǎng)絡(luò)應(yīng)盡可能靠近接收器輸入端.

正在載入評(píng)論數(shù)據(jù)...

此文關(guān)鍵字: LVDS振蕩器SiTime差分振蕩器

相關(guān)資訊

- [2023-09-05]家用電器依賴(lài)Jauch晶振

- [2023-09-01]IQD常見(jiàn)問(wèn)題

- [2023-06-29]6G小體積Q26.0-JXS21-12-10/20-...

- [2023-06-28]6G晶振X1G0036910116晶體振蕩器...

- [2020-07-07]TXC晶振強(qiáng)大之處原來(lái)可以從這點(diǎn)...

- [2019-08-26]電子書(shū)籍市場(chǎng)的晶振器件需具備小...

- [2019-08-22]低ESR50兆赫晶振優(yōu)化性能

- [2019-08-13]為了您的應(yīng)用選擇合適的晶振請(qǐng)仔...