企業(yè)博客

更多>>石英晶體振蕩器輸出邏輯

來源:http://www.fengxong.cn 作者:康比電子 2019年03月18

隨著下一代串行標(biāo)準(zhǔn)數(shù)據(jù)速率的增加,模擬異常對信號完整性和質(zhì)量的影響比以往任何時候都大.信號路徑中的導(dǎo)體,包括電路板走線,過孔,連接器和電纜,表現(xiàn)出更大的傳輸線效應(yīng),回波損耗和反射會降低信號電平,引起偏斜,并增加噪聲和抖動.然而,一切都從基本系統(tǒng)時鐘信號開始,下面康比電子簡單簡述一下關(guān)于的Pletronics Crystal的SYSCLK發(fā)起方法.

SYSCLK發(fā)起方法

基本的"無褶邊"晶體振蕩器使用石英晶體,并與簡單電路一起使用,以晶體的基本模式運行,產(chǎn)生方波輸出.這種架構(gòu)為峰值和均方根抖動提供了最佳性能,通常在高達50Mhz的頻率下成本效益最高.為了以盡可能最低的抖動達到更高的頻率,使用了一種被稱為高頻基波的技術(shù).晶體可以以其泛音模式之一振動,泛音模式出現(xiàn)在基頻諧振頻率的奇數(shù)倍附近.這種晶體被稱為第三,第五,第七…等泛音晶體.為此,振蕩器電路通常包括額外的設(shè)計元件,以選擇所需的泛音.相關(guān)地,在典型應(yīng)用中,可以有效地執(zhí)行一種架構(gòu),該架構(gòu)使晶體在其第三泛音上工作,以達到高達3x50Mhz=150Mhz的頻率.

在較高泛音上工作需要復(fù)雜得多的電路,幾家振蕩器公司正在努力增加石英晶振基波和第三泛音諧振技術(shù),以支持例如70.8333Mhzx3=212.500Mhz的10Gb光纖通道.這些努力集中在隨著數(shù)據(jù)總線速度不斷提高而提供所需的最低抖動主時鐘性能.盡管如此,這項技術(shù)仍處于先進階段,并不容易從所有晶體振蕩器供應(yīng)商處獲得.

另一種已經(jīng)成功利用的技術(shù)是集成整數(shù)乘法器.在這些器件中,通過將輸入信號鎖定到以晶體頻率的直接整數(shù)倍(2x,3x,4x…等)運行的集成壓控振蕩器來提高頻率,然后將其二次分頻回所需的工作頻率.可以采用的另一種方法是諧波乘法.這在技術(shù)上類似于晶體泛音的利用,不同之處在于晶體振蕩器(不是晶體)的輸出信號乘以整數(shù)值.除了電路集成中的損耗和其他折衷之外,抖動性能比直接(即泛音模式的晶體基礎(chǔ))頻率產(chǎn)生惡化了20倍.

因此,雖然基頻,泛音和/或諧波頻率的產(chǎn)生是可能的,但是與能夠滿足抖動要求的積分整數(shù)乘法相比,這些技術(shù)通常成本較高且復(fù)雜度過高.為了避免任何不必要的成本溢價,設(shè)計人員在設(shè)計余量微調(diào)期間需要關(guān)注的是計算輸出信號抖動的特定帶寬.

使用的第三種技術(shù)被稱為集成的"分數(shù)N"乘法器.在這里,輸入信號的頻率實際上可以轉(zhuǎn)換成任何其他頻率——整數(shù)相關(guān)或無關(guān).例如,25Mhz晶體頻率可以通過25.78125的分數(shù)乘法轉(zhuǎn)換為644.53125Mhz.出于超出本文預(yù)期目的和深度的原因,這導(dǎo)致了最高的信號抖動量.同樣,對于某些系統(tǒng)來說,這也足夠了,而且在215Mhz以上的頻率下使用也是最具成本效益的. 晶體振蕩器輸出邏輯

上一節(jié)討論了產(chǎn)生CLK的方法及其對抖動性能的影響.無論實現(xiàn)架構(gòu)是基頻還是泛音晶振,倍頻器還是分數(shù)倍頻器,晶振還包含符合現(xiàn)有邏輯技術(shù)的輸出驅(qū)動器.輸出邏輯兼容性的具體類型可以是低壓CMOS,低壓,正電源發(fā)射耦合邏輯,低壓差分信號和/或高速電流控制邏輯.輸出邏輯類型主要與給定應(yīng)用類型內(nèi)的處理設(shè)備的輸出頻率和/或邏輯接口的通用性相關(guān).例如,PCIeSYSCLKs的主要邏輯類型是HCSL.晶體振蕩器輸出邏輯兼容性通常比處理設(shè)備邏輯開發(fā)滯后6到12個月,有時甚至更長.在此期間使用邏輯翻譯器.這方面的一個例子是傳輸最小化差分信號(TMDS).TMDS在系統(tǒng)設(shè)計(如HDMI)的某些應(yīng)用中被采用,但目前不能作為晶體振蕩器輸出邏輯的選擇.輸出邏輯類型的重要意義在于通過將晶體振蕩器(以及任何額外的輸出轉(zhuǎn)換設(shè)備)連接到處理設(shè)備而引入的"接口抖動".通常,通過"眼圖"轉(zhuǎn)換時間最快的邏輯類型(例如上升/下降時間)將導(dǎo)致最低的接口抖動.

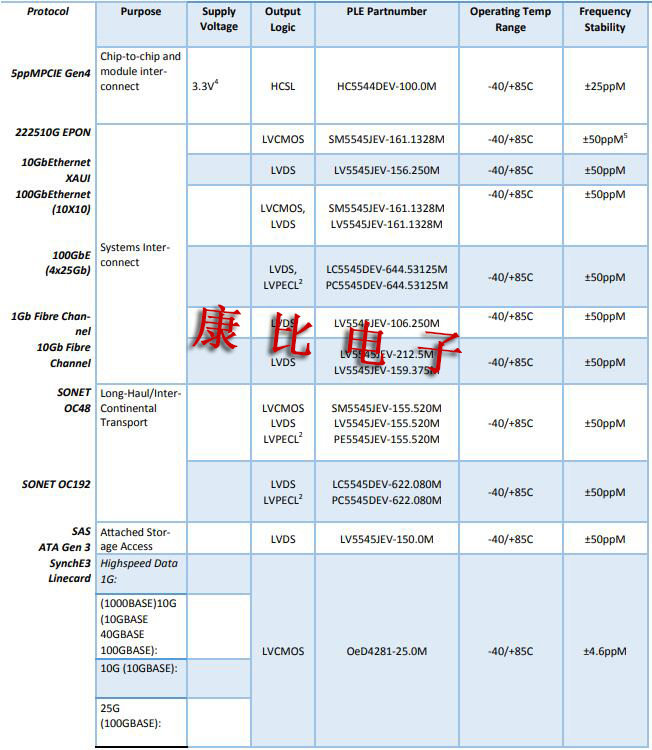

在Pletronics Crystal我們提供包含上述每種技術(shù)的解決方案:高頻晶體基波,泛音,積分和分數(shù).每種產(chǎn)品的執(zhí)行都是為了向客戶提供成本和性能最有效的解決方案.表1列出了當(dāng)今最流行的串行數(shù)據(jù)協(xié)議所采用的技術(shù).表2包含了系統(tǒng)設(shè)計物料清單中可以調(diào)用的具體零件號.同任何一家市場領(lǐng)先的公司一樣,普列特尼克公司的產(chǎn)品也在不斷發(fā)展,努力讓我們的客戶保持競爭優(yōu)勢.

不管性能規(guī)格,規(guī)格要求或具體的物理層芯片組/執(zhí)行方法如何,最重要的規(guī)格是實現(xiàn)的成本效益.滿足所有性能要求但總成本高于市場要求的所有商業(yè)和工業(yè)系統(tǒng)都沒有價值.所有高質(zhì)量石英晶體振蕩器供應(yīng)商在其數(shù)據(jù)手冊中發(fā)布的抖動生成規(guī)范中都包含一定量的保護帶.因為,有充分的理由,系統(tǒng)設(shè)計者在他們要求的規(guī)格中也包括一定數(shù)量的保護帶,與聲譽良好的晶體振蕩器制造商合作可能會導(dǎo)致雙重保護帶,因此解決方案成本過高.為了幫助指定合適的振蕩器,而不增加過多的保護帶和成本,表1顯示了當(dāng)今最流行的數(shù)據(jù)/通信應(yīng)用.

SYSCLK發(fā)起方法

基本的"無褶邊"晶體振蕩器使用石英晶體,并與簡單電路一起使用,以晶體的基本模式運行,產(chǎn)生方波輸出.這種架構(gòu)為峰值和均方根抖動提供了最佳性能,通常在高達50Mhz的頻率下成本效益最高.為了以盡可能最低的抖動達到更高的頻率,使用了一種被稱為高頻基波的技術(shù).晶體可以以其泛音模式之一振動,泛音模式出現(xiàn)在基頻諧振頻率的奇數(shù)倍附近.這種晶體被稱為第三,第五,第七…等泛音晶體.為此,振蕩器電路通常包括額外的設(shè)計元件,以選擇所需的泛音.相關(guān)地,在典型應(yīng)用中,可以有效地執(zhí)行一種架構(gòu),該架構(gòu)使晶體在其第三泛音上工作,以達到高達3x50Mhz=150Mhz的頻率.

在較高泛音上工作需要復(fù)雜得多的電路,幾家振蕩器公司正在努力增加石英晶振基波和第三泛音諧振技術(shù),以支持例如70.8333Mhzx3=212.500Mhz的10Gb光纖通道.這些努力集中在隨著數(shù)據(jù)總線速度不斷提高而提供所需的最低抖動主時鐘性能.盡管如此,這項技術(shù)仍處于先進階段,并不容易從所有晶體振蕩器供應(yīng)商處獲得.

另一種已經(jīng)成功利用的技術(shù)是集成整數(shù)乘法器.在這些器件中,通過將輸入信號鎖定到以晶體頻率的直接整數(shù)倍(2x,3x,4x…等)運行的集成壓控振蕩器來提高頻率,然后將其二次分頻回所需的工作頻率.可以采用的另一種方法是諧波乘法.這在技術(shù)上類似于晶體泛音的利用,不同之處在于晶體振蕩器(不是晶體)的輸出信號乘以整數(shù)值.除了電路集成中的損耗和其他折衷之外,抖動性能比直接(即泛音模式的晶體基礎(chǔ))頻率產(chǎn)生惡化了20倍.

因此,雖然基頻,泛音和/或諧波頻率的產(chǎn)生是可能的,但是與能夠滿足抖動要求的積分整數(shù)乘法相比,這些技術(shù)通常成本較高且復(fù)雜度過高.為了避免任何不必要的成本溢價,設(shè)計人員在設(shè)計余量微調(diào)期間需要關(guān)注的是計算輸出信號抖動的特定帶寬.

使用的第三種技術(shù)被稱為集成的"分數(shù)N"乘法器.在這里,輸入信號的頻率實際上可以轉(zhuǎn)換成任何其他頻率——整數(shù)相關(guān)或無關(guān).例如,25Mhz晶體頻率可以通過25.78125的分數(shù)乘法轉(zhuǎn)換為644.53125Mhz.出于超出本文預(yù)期目的和深度的原因,這導(dǎo)致了最高的信號抖動量.同樣,對于某些系統(tǒng)來說,這也足夠了,而且在215Mhz以上的頻率下使用也是最具成本效益的. 晶體振蕩器輸出邏輯

上一節(jié)討論了產(chǎn)生CLK的方法及其對抖動性能的影響.無論實現(xiàn)架構(gòu)是基頻還是泛音晶振,倍頻器還是分數(shù)倍頻器,晶振還包含符合現(xiàn)有邏輯技術(shù)的輸出驅(qū)動器.輸出邏輯兼容性的具體類型可以是低壓CMOS,低壓,正電源發(fā)射耦合邏輯,低壓差分信號和/或高速電流控制邏輯.輸出邏輯類型主要與給定應(yīng)用類型內(nèi)的處理設(shè)備的輸出頻率和/或邏輯接口的通用性相關(guān).例如,PCIeSYSCLKs的主要邏輯類型是HCSL.晶體振蕩器輸出邏輯兼容性通常比處理設(shè)備邏輯開發(fā)滯后6到12個月,有時甚至更長.在此期間使用邏輯翻譯器.這方面的一個例子是傳輸最小化差分信號(TMDS).TMDS在系統(tǒng)設(shè)計(如HDMI)的某些應(yīng)用中被采用,但目前不能作為晶體振蕩器輸出邏輯的選擇.輸出邏輯類型的重要意義在于通過將晶體振蕩器(以及任何額外的輸出轉(zhuǎn)換設(shè)備)連接到處理設(shè)備而引入的"接口抖動".通常,通過"眼圖"轉(zhuǎn)換時間最快的邏輯類型(例如上升/下降時間)將導(dǎo)致最低的接口抖動.

在Pletronics Crystal我們提供包含上述每種技術(shù)的解決方案:高頻晶體基波,泛音,積分和分數(shù).每種產(chǎn)品的執(zhí)行都是為了向客戶提供成本和性能最有效的解決方案.表1列出了當(dāng)今最流行的串行數(shù)據(jù)協(xié)議所采用的技術(shù).表2包含了系統(tǒng)設(shè)計物料清單中可以調(diào)用的具體零件號.同任何一家市場領(lǐng)先的公司一樣,普列特尼克公司的產(chǎn)品也在不斷發(fā)展,努力讓我們的客戶保持競爭優(yōu)勢.

表-管道末端裝置零件號

選擇最佳時鐘起始設(shè)備不管性能規(guī)格,規(guī)格要求或具體的物理層芯片組/執(zhí)行方法如何,最重要的規(guī)格是實現(xiàn)的成本效益.滿足所有性能要求但總成本高于市場要求的所有商業(yè)和工業(yè)系統(tǒng)都沒有價值.所有高質(zhì)量石英晶體振蕩器供應(yīng)商在其數(shù)據(jù)手冊中發(fā)布的抖動生成規(guī)范中都包含一定量的保護帶.因為,有充分的理由,系統(tǒng)設(shè)計者在他們要求的規(guī)格中也包括一定數(shù)量的保護帶,與聲譽良好的晶體振蕩器制造商合作可能會導(dǎo)致雙重保護帶,因此解決方案成本過高.為了幫助指定合適的振蕩器,而不增加過多的保護帶和成本,表1顯示了當(dāng)今最流行的數(shù)據(jù)/通信應(yīng)用.

正在載入評論數(shù)據(jù)...

此文關(guān)鍵字: 石英晶體振蕩器輸出時鐘振蕩器設(shè)備

相關(guān)資訊

- [2024-02-18]Greenray晶體振蕩器專為國防和航...

- [2024-01-20]HELE加高產(chǎn)品和技術(shù)及熱門應(yīng)用

- [2024-01-20]HELE加高一個至關(guān)重要的組件晶體...

- [2023-12-28]Suntsu晶振最新的射頻濾波器突破...

- [2023-12-28]Qantek提供各種高可靠性微處理器...

- [2023-10-11]日本納卡石英晶體的低老化領(lǐng)先同...

- [2023-09-25]遙遙領(lǐng)先H.ELE開啟汽車創(chuàng)新

- [2023-09-23]瑞薩電子MCU和MPU產(chǎn)品領(lǐng)先同行